In collaboration with

# ENA303 ARTIC R2 User Datasheet

For use with Argos 2/3/4

File Name: ARTIC\_R2\_Datasheet\_1v10

Doc. version date: Contact: 21-Jan-20 info@kineis.com

AnSem NV - Researchpark Haasrode 1113 - Esperantolaan 9 - 3001 Heverlee - Belgium AnSem BV - Pantheon 20 - 7521 PR Enschede - The Netherlands www.ansem.com Table of Contents

| Revisi | on history                        | iv |

|--------|-----------------------------------|----|

| Refere | nces                              | iv |

| Glossa | ary                               | V  |

| 1. Dev | vice Information                  | 7  |

| 1.1    | Pad Assignments                   | 7  |

| 1.2    | Pin Descriptions                  | 8  |

| 1.3    | Package dimensions                | 9  |

| 1.4    | Storage                           | 10 |

| 1.5    | Soldering                         | 10 |

| 1.6    | Typical usage                     |    |

| 2. Ele | ctrical Characteristics           |    |

| 2.1    | Absolute Maximum Ratings          |    |

| 2.2    | Electrical Characteristics        | 12 |

| 2.3    | SPI Interface                     | 14 |

| 2.4    | ARTIC Memories                    |    |

| 2.5    | Boot configuration                | 18 |

| 2.6    | Bias                              |    |

| 2.7    | Reset                             |    |

| 2.8    | GPIO                              |    |

| 2.9    | Flash interface                   |    |

| 2.10   | TCXO interface                    |    |

| 3. Ope | erating the device                |    |

| 3.1    | Start-up sequence                 |    |

| 3.2    | Firmware status - interrupt flags | 21 |

| 3.3    | MCU commands                      | 22 |

| 3.4    | Memory locations                  | 27 |

| 3.5    | Transmission                      | 28 |

| 3.6    | Reception                         | 32 |

| 3.7    | CRC Check                         |    |

| 3.8    | Firmware version                  | 35 |

| 3.9    | TCXO control feature              | 36 |

| 3.10   | GPIO                              | 36 |

| 3.11   | Power consumption                 | 37 |

| 3.12   | Timing transmission and receiving | 38 |

| 3.13   | Packet timing                     | 38 |

### ENA303 ARTIC R2 User Datasheet - For use with Argos 2/3/4

| 40 |

|----|

|    |

| 42 |

| 42 |

| 42 |

|    |

# **Revision history**

| V    | Date       | Sections<br>concerned | Info                                                                             |  |

|------|------------|-----------------------|----------------------------------------------------------------------------------|--|

| 1v0  | 2016-10-25 | all                   | first version                                                                    |  |

| 1v1  | 2017-03-02 | 1.3                   | Added Package dimensions                                                         |  |

| 1v2  | 2017-08-02 | 3.1,3.5,3.6,3.11      | Startup time, Transmit frequency, Satellite detection flag, current consumption. |  |

| 1v3  | 2017-12-01 | 1                     | Added storage and soldering information                                          |  |

| 1v4  | 2018-03-16 | 1.3,4                 | Added typical usage, layout guidelines                                           |  |

| 1v5  | 2018-04-24 | 1                     | Added build of material                                                          |  |

| 1v6  | 2018-06-04 | 3.5.3,                | Transmission bands                                                               |  |

| 1v7  | 2019-10-15 | 1.4                   | Storage conditions adapted                                                       |  |

| 1v8  | 2019-10-23 | 3.9                   | TCXO control feature extended                                                    |  |

| 1v9  | 2019-12-20 | 1.6                   | Added Reference to ARTIC_evaluation_board                                        |  |

| 1v10 | 2020-01-16 | 3.12, 3.13            | Added transmission, receiving and packet timing                                  |  |

# References

**AD1** Platform Transmitter Terminal (PTT-A2), Platform Message Transceiver (PMT-A2) - Physical Layer System Requirements. - 19/01/2016. - Vol. v5.0.

**AD2** Platform Transmitter Terminal (PTT-A3, including PTT-ZE), Platform Message Transceiver (PMT-A3) - Physical Layer System Requirements. - 19/01/2016. - Vol. v5.0.

**AD3** Platform Transmitter Terminal (PTT-HD A3), Platform Message Transceiver (PMT-HD A3) - Physical Layer System Requirements. - 19/01/2016. - Vol. v5.0.

**AD4** Very Low Data Rate Platform Transmitter Terminal for ARGOSs 4 (PTT-VLD-A4) - Physical Layer System Requirements. - 19/01/2016. - Vol. v2.0.

**AD5** High Data Rate Platform Transmitter Terminal For ARGOS 4 (PTT/PMT-HD-A4) - Physical Layer System Requirements. - 19/01/2016. - Vol. v2.0.

**AD6** Receiver Terminal for ARGOS 3 – Physical Layer System Requirements. - 19/01/2016. - Vol. v3.0.

**AD7** Receiver Terinal for ARGOS 4 – Physical Layer System Requirements. - 19/01/2016. - Vol. v1.6.

AD8 Services and Message Formats, General Specifications. - 21/03/2019. - Vol. v1.6.

AD9 Certification of PTT and PMT. - 28/08/2006. - Vol. v2.0.

AnSem ARTIC\_evaluation\_board\_1v4, [Report]. - 20/12/2019.

# Glossary

| ACK           | Acknowledge                                                                                   |

|---------------|-----------------------------------------------------------------------------------------------|

| ADC           | Analog-to-Digital Converter                                                                   |

| ARGOS         | Advanced Research and Global Observation Satellite                                            |

| ASCII         | American Standard Code for Information Interchange                                            |

| bps           | Bits per second                                                                               |

| BPSK          | Binary Phase-Shift Keying                                                                     |

| C/S @         | Spacecraft address                                                                            |

| CNES          | Centre National d'Etudes Spatiales                                                            |

| COSPAS-SARSAT | Cosmitscheskaja Sistema Poiska Awarinitsch Sudow - Search And Rescue Satellite Aided Tracking |

| CRC           | Cyclic Redundancy Check                                                                       |

| DSP           | Digital Signal Processor                                                                      |

| DSSS          | Direct Sequence Spread Spectrum                                                               |

| FCS           | Frame Check Sequence                                                                          |

| GMSK          | Gaussian Minimum Shift Keying                                                                 |

| GND           | Ground connection                                                                             |

| GNSS          |                                                                                               |

|               | Global Navigation Satellite System                                                            |

| GPIO          | General Purpose Input Output                                                                  |

| GPS           | Global Positional System                                                                      |

| HAD           | High Definition Audio                                                                         |

| HD            | High data rate                                                                                |

| INT1, INT2    | Interrupt lines                                                                               |

| LSB           | Least Significant Bit                                                                         |

| LSBit         | Least Significant Byte                                                                        |

| LUT           | LookUp Table                                                                                  |

| MCU           | Microcontroller Unit                                                                          |

| MISO          | Master In Slave Out (Serial Peripheral Interface)                                             |

| MOSI          | Master Out Slave In (Serial Peripheral Interface)                                             |

| MSB           | Most Significant Byte                                                                         |

| MSBit         | Most Significant Bit                                                                          |

| MSL           | Moisture Sensitivity Level                                                                    |

| NACK          | Negative Acknowledge                                                                          |

| NMEA          | National Marine Electronics Association                                                       |

| OQPSK         | Offset Quadrature Phase Shift Keying                                                          |

| OTP           | One Time Programmable memory                                                                  |

| РА            | Power Amplifier                                                                               |

| РСВ           | Printed Circuit Board                                                                         |

| PMT           | Platform Message Transceiver                                                                  |

| PTT           | Platform Transmitter Terminal                                                                 |

| QFN           | Quad Flat No-leads package                                                                    |

| QPSK          | Quadrature Phase-Shift Keying                                                                 |

| RS-232        | Recommended Standard 232 in telecommunications                                                |

| RX            | Receiver                                                                                      |

| RXIN          | Receiver input signal                                                                         |

| SCLK          | Serial Clock                                                                                  |

| SPI           | Serial Peripheral Interface                                                                   |

| SSB           | Single Side Band                                                                              |

| SSN           | Slave Select Not                                                                              |

| тсхо          | Temperature Compensated Xtal Oscillator                                                       |

| TTL           | Transistor-Transistor Logic                                                                   |

| тх            | Transmitter                                                                                   |

| UART          | Universal Asynchronous Receiver-Transmitter                                                   |

| VLD           | Very low datarate                                                                             |

|               |                                                                                               |

# **General description**

The ARTIC is an integrated low power small size ARGOS • 2/3/4 single chip radio. ARTIC implements a message based wireless interface. For satellite uplink communication, ARTIC will encode, modulate and transmit provided user messages. For downlink communication, ARTIC will lock to the downstream, demodulate and . decode and extract the satellite messages.

The ARTIC can transmit signals in frequency bands around 400MHz and receive signals in the bands around 466MHz, with the ARGOS satellite in accordance system specifications.

The ARTIC is compliant and certified for all ARGOS 2 and • ARGOS 3 TX standards. It contains a RF transceiver, a frequency synthesiser and a digital baseband modem. The ARTIC contains an on-chip power amplifier delivering 1mW [0dBm] output power, that serves as an output for connecting an external high efficient PA. The (de)modulation algorithms run on an on-chip DSP. This • software approach allows for retargeting the ARTIC for . other applications. The DSP program can be retained on an external flash or the MCU.

Internal power management is autonomously handled by Applications ARTIC in order to optimize its current consumption.

The ARTIC can communicate with an external microcontroller using a standard SPI interface.

The ARTIC chip is a QFN48, 7mm x 7mm, 0.5mm pitch.

# **Features**

- Serial interface (SPI) for communication with MCU

- Programmable DSP core on board to ensure flexibility

- RX frequency : 466MHz TX frequency: 400MHz

- Fractional N frequency synthesis

- Supported TX standards:

- BPSK: PTT-A2 (ARGOS 2), PTT-VLD (ARGOS 4), COSPAS-SARSAT 1e Gen<sup>1</sup>.

- QPSK: PTT-A3, PTT-ZE (ARGOS 3).

- GMSK: PTT-HD (ARGOS3), PTT-MD (ARGOS4), 0 PTT-HD (ARGOS4)

- Supported RX standards:

- QPSK: PMT-A3 (ARGOS 3)

- DSSS OQPSK: PMT-A4 (ARGOS 4) 0

- Dedicated flash Interface to retain Firmware.

- Support COSPAS-SARSAT standard

- Operates on external 26MHz reference clock

- Dual supply, 1.8V and 3.3V

- Integrated PA (0dBm) to combine with external PA

- Pop up tags for animal tracking

- Buoys and floats, Maritime security

- Satellite-based vessel monitoring system (VMS)

- Tracking of adventurers and yacht racing

- Search and rescue (COSPAS-SARSAT)

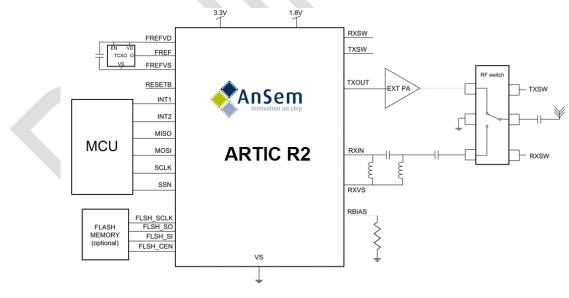

# **Functional Block Diagram**

Figure 1 Functional Block Diagram

<sup>1</sup> Not yet supported in R2

# 1. Device Information

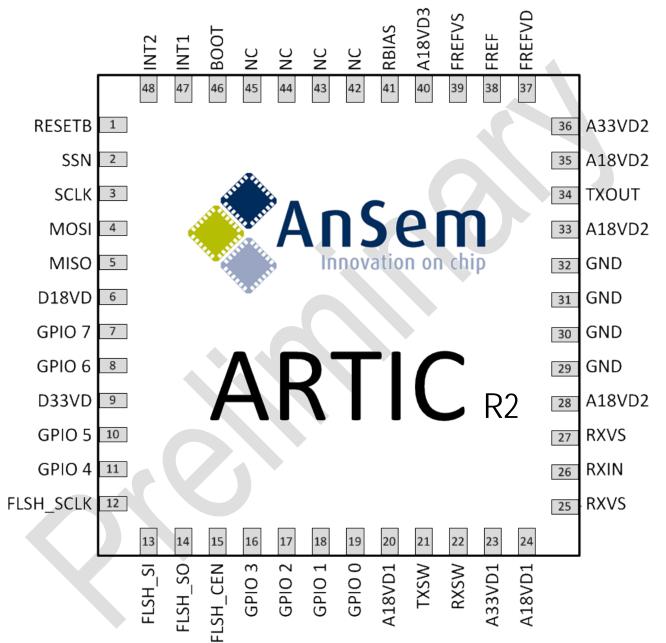

## 1.1 Pad Assignments

The ARTIC is assembled in a 7mm by 7mm, 48 lead QFN package, and 0.5mm pitch

## 1.2 Pin Descriptions

| Pin   | Name     | Description                      | Voltage domain |

|-------|----------|----------------------------------|----------------|

| 1     | RESETB   | Global chip reset                | 3.3V           |

| 2     | SSN      | SPI slave select                 | 3.3V           |

| 3     | SCLK     | SPI clock                        | 3.3V           |

| 4     | MOSI     | SPI master out slave in pin      | 3.3V           |

| 5     | MISO     | SPI master in slave out pin      | 3.3V           |

| 6     | D18VD    | Digital 1.8V supply              | 1.8V           |

| 7     | GPIO 7   | General purpose input/output pin | 3.3V           |

| 8     | GPIO 6   | General purpose input/output pin | 3.3V           |

| 9     | D33VD    | Digital 3.3V supply              | 3.3V           |

| 10    | GPIO 5   | General purpose input/output pin | 3.3V           |

| 11    | GPIO 4   | General purpose input/output pin | 3.3V           |

| 12    | FLSH_SLK | SPI Flash clock                  | 3.3V           |

| 13    | FLSH_SI  | SPI Flash slave in pin           | 3.3V           |

| 14    | FLSH_SO  | SPI Flash slave out pin          | 3.3V           |

| 15    | FLSH CEN | SPI Flash slave select           | 3.3V           |

| 16    | GPIO 3   | General purpose input/output pin | 3.3V           |

| 17    | GPIO 2   | General purpose input/output pin | 3.3V           |

| 18    | GPIO 1   | General purpose input/output pin | 3.3V           |

| 19    | GPIO 0   | General purpose input/output pin | 3.3V           |

| 20    | A18VD1   | Analog 1.8V supply               | 1.8V           |

| 21    | TXSW     | Transmit switch control signal   | 3.3V           |

| 22    | RXSW     | Receive switch control signal    | 3.3V           |

| 23    | A33VD1   | Analog 3.3V supply               | 3.3V           |

| 24    | A18VD1   | Analog 1.8V supply               | 1.8V           |

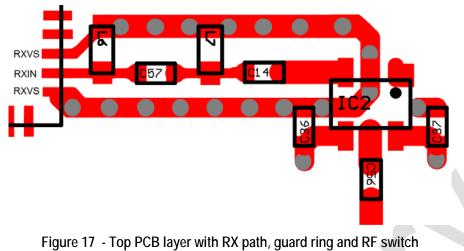

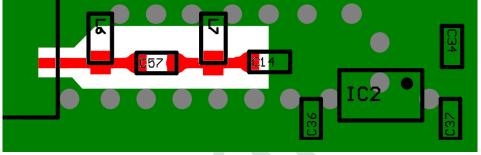

| 25    | RXVS     | RX input ground pin              | 1.8V           |

| 26    | RXIN     | RX input                         | 1.8V           |

| 27    | RXVS     | RX input ground pin              | 1.8V           |

| 28    | A18VD2   | Analog 1.8V supply               | 1.8V           |

| 29-32 | VSS      | Ground connection                | 1              |

| 33    | A18VD2   | Analog 1.8V supply               | 1.8V           |

| 34    | TXOUT    | Low power PA output              | 1.8V           |

| 35    | A18VD2   | Analog 1.8V supply               | 1.8V           |

| 36    | A33VD2   | Analog 3.3V supply               | 3.3V           |

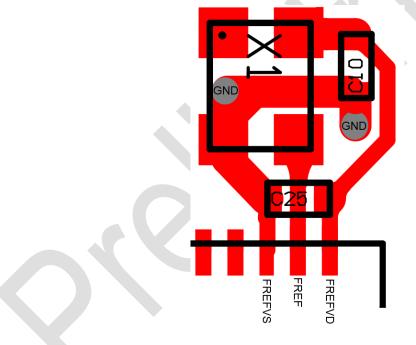

| 37    | FREFVD   | TCXO supply                      | 1.8V           |

| 38    | FREF     | TCXO input                       | 1.8V           |

| 39    | FREFVS   | TCXO ground                      | 1.8V           |

| 40    | A18VD3   | Analog 1.8V supply               | 1.8V           |

| 41    | RBIAS    | External bias resistor           | 1.8V           |

| 42-45 | NC       | Not connected                    | -              |

| 46    | BOOT     | Digital 3.3V input               | 3.3V           |

| 47    | INT1     | Interrupt 1                      | 3.3V           |

| 48    | INT2     | Interrupt 2                      | 3.3V           |

| PAD   | VSS      | Ground connection                | GND            |

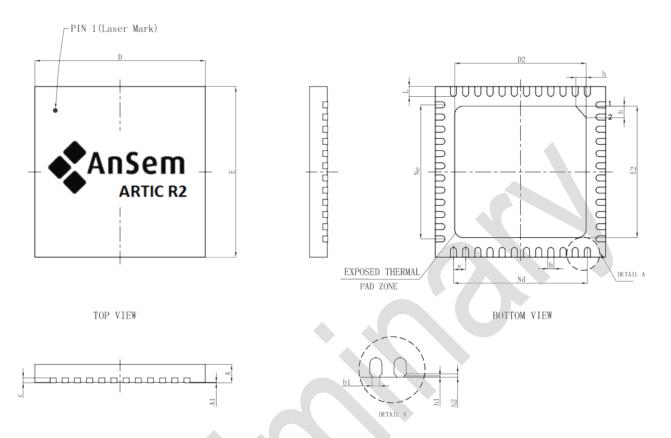

## 1.3 Package dimensions

|   | Symbol | Milli        | imetres     | 5    |  |  |  |  |

|---|--------|--------------|-------------|------|--|--|--|--|

|   |        | Min          | Nom         | Max  |  |  |  |  |

|   | A      | 0.70         | 0.75        | 0.8  |  |  |  |  |

|   | A1     | -            | 0.02        | 0.05 |  |  |  |  |

|   | b      | 0.18         | 0.25        | 0.30 |  |  |  |  |

|   | b1     | 0.21         |             |      |  |  |  |  |

|   | С      | 0.18         | 0.20        | 0.23 |  |  |  |  |

|   | D      | 6.90         | 7.00        | 7.10 |  |  |  |  |

|   | D2     | 5.50         | 5.60        | 5.70 |  |  |  |  |

|   | е      | 0.5          | 50BSC       |      |  |  |  |  |

|   | Ne     | 5.5          | 50BSC       |      |  |  |  |  |

|   | Nd     | 5.5          | 50BSC       |      |  |  |  |  |

|   | E      | 6.90         | 7.00        | 7.10 |  |  |  |  |

|   | E2     | E2 5.50 5.60 |             |      |  |  |  |  |

|   | L      | 0.35         | 0.40        | 0.45 |  |  |  |  |

| h |        | 0.30         | 0.35        | 0.40 |  |  |  |  |

|   | h1     | 0.0          | 3REF        |      |  |  |  |  |

|   | h2     | 0.1          | <b>OREF</b> |      |  |  |  |  |

|   |        |              |             |      |  |  |  |  |

Confidential ©

### 1.4 Storage

The packages have a Moisture Sensitivity Level (MSL) rating of 3; please see the latest IPC/JEDEC J-STD-033 standard for MSL description and MSL 3 bake conditions.

Maximum recommended shelf life for dry packed SMD packages shall be a minimum of 12 months from the bag seal date, when stored in a noncondensing atmospheric environment of <40°C/90% RH.

For an unopened bag, packaged in a sealed MBB (Moisture Barrier Bags) with desiccant, the shelf life of SMD is greater than 5 years for MSL 3 parts. This assumes that the MBB remains intact; therefore, double-bagging is recommended for extremely long-term storage.

Maximum recommended shelf life in unsealed/exposed to oxygen packaging is 6 months.

Floor Life (out of bag) at factory ambient  $\leq$ 30°C/60% RH: MSL3: 168 hours. After bag is opened, devices that will be subjected to reflow solder or other high temperature process must be mounted within 168 hours of factory conditions  $\leq$ 30°C/60% RH.

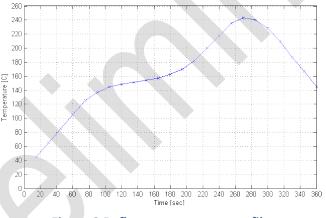

### 1.5 Soldering

Reflow soldering with long industrial convection ovens is the preferred method of soldering the ARTIC chip to a printed circuit board or PCB. The temperature profile in Figure 2 acts as a temperature guideline for soldering the ARTIC QFN. The required peak temperature is 240±5°C.

Figure 2 Reflow temperature profile

### 1.6 Typical usage

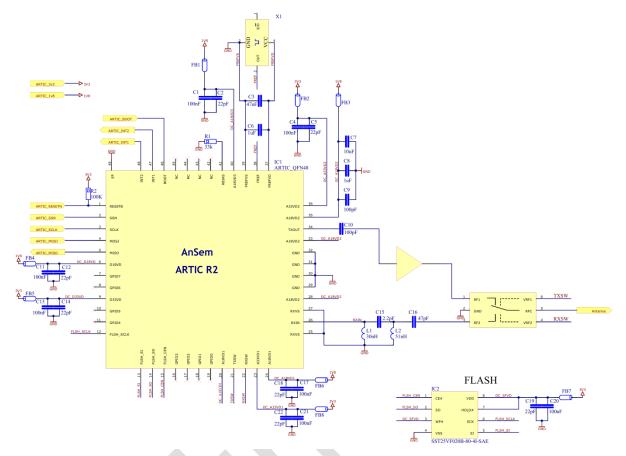

Figure 3 Typical usage of the ARTIC chip

## Build of material:

| Designator                           | Qty | Manufact | Part number           | Cap.  | Volt. | Res. | Ind. | Curr. | Tol. |

|--------------------------------------|-----|----------|-----------------------|-------|-------|------|------|-------|------|

| Designator                           | QLY |          | Fart number           | Cap.  | VOIL. | Res. | mu.  | Curr. | 101. |

|                                      | •   | urer     |                       |       |       |      |      | 000 4 | 050/ |

| FB1, FB2, FB4, FB5, FB6,<br>FB7, FB8 | 7   | MUR      | BLM15AG221SN1D        |       |       |      |      | 300mA | 25%  |

| FB3                                  | 1   | MUR      | BLM15EG221SN1D        |       |       |      |      | 700mA | 25%  |

| IC1                                  | 1   | ANS      | ARTIC_QFN48           |       |       |      |      |       |      |

| IC2                                  | 1   | MIC      | SST25VF020B-80-4I-SAE |       |       |      |      |       |      |

| X1                                   | 1   | KYOCERA  |                       |       | 1.8V  |      |      |       |      |

| C1, C4, C11, C13, C17,<br>C20, C21   | 7   | XXX      | MC0402B104K160CT      | 100nF | 16V   |      |      |       | 10%  |

| C9, C10                              | 2   | MUL      | MC000274              | 100pF | 50V   |      |      |       | 5%   |

| C7                                   | 1   | AVX      | C1005X5R0J106M050BC   | 10uF  | 6V3   |      |      |       | 20T  |

| C6, C8                               | 2   | MUR      | GRM155R60J105KE19D    | 1uF   | 6.3V  |      |      |       | 10T  |

| C15                                  | 1   | MUL      | MC000282              | 2.2pF | 50V   |      |      |       | 2.3% |

| C2, C5, C12, C14, C18,               | 7   | MUL      | CBR04C220J5GAC        | 22pF  | 50V   |      |      |       | 5%   |

| C19, C22                             |     |          |                       |       |       |      |      |       |      |

| C3                                   | 1   | MUR      | GRM155R71C473KA01D    | 47nF  | 16V   |      |      |       | 10T  |

| C16                                  | 1   | KER      | CBR04C470F3GAC        | 47pF  | 25V   |      |      |       | 1%   |

| L1                                   | 1   | CLC      | 0402HP-30NXGLU        |       |       | 0.35 | 30nH | 450mA | 2%   |

| L2                                   | 1   | CLC      | 0402HP-51NXGLU        |       |       | 0.7R | 51nH | 360mA | 2%   |

| R1                                   | 1   | YAG      | RC0402FR-0733KL       |       |       | 33k  |      |       | 1%   |

| R2                                   | 1   | MUL      | MCMR04X1003FTL        |       |       | 100K |      |       | 1%   |

Note:

More information on the external amplifier and RF switch can be found in the report (AnSem, 20/12/2019).

# 2. Electrical Characteristics

### 2.1 Absolute Maximum Ratings

|                                                                      | VALUE       | UNIT |

|----------------------------------------------------------------------|-------------|------|

| Supply voltage, A33VD1, A33VD2, D33VD with respect to VSS            | 0 to 3.63V  | V    |

| Supply voltage, A18VD1, A18VD2, A18VD3 and D18VD with respect to VSS | 0 to 1.9V   | V    |

| RXIN input power                                                     | 10          | dBm  |

| Power consumption                                                    | 300         | mW   |

| Maximal junction temperature                                         | +125        | °C   |

| Storage temperature range                                            | -40 to +125 | °C   |

| Operating temperature range                                          | -40 to +85  | °C   |

If stresses are applied that are beyond those listed above permanent damage may be caused to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may degrade device reliability.

### 2.2 Electrical Characteristics

(A18VD1 = A18VD2 = A18VD3 = D18VD = 1.8V, A33VD1 = A33VD2 = D33VD = 3.3V, Tj = -40 to +85°C, unless otherwise noted. Typical values are at Tj = 25°C)

#### 2.2.1 Receiver

#### 2.2.1 a) Argos3

| PARAMETER               | CONDITIONS                                                                                                 | MIN  | TYP | MAX  | UNIT   |

|-------------------------|------------------------------------------------------------------------------------------------------------|------|-----|------|--------|

| Input power level       |                                                                                                            |      |     |      | dBm    |

| ARGOS 3 normal mode     | $Tj = 25^{\circ}C$                                                                                         | -126 |     | -112 |        |

| ARGOS 3 backup mode     | Tj = 25°C                                                                                                  | -128 |     | -112 |        |

| Noise figure            | Tj = 25°C                                                                                                  |      |     | 5.7  | dB     |

| ADC resolution          |                                                                                                            |      | 7   |      | Bits   |

| ADC sampling frequency  |                                                                                                            |      | 650 |      | kHz    |

| Allowed spurious levels | For f at f <sub>c</sub> +15kHz>f>f <sub>c</sub> -<br>15kHz                                                 |      |     | -145 | dBm    |

|                         | For f:<br>f <sub>c</sub> +200kHz>f>f <sub>c</sub> +50kHz<br>f <sub>c</sub> -50kHz>f>f <sub>c</sub> -200kHz |      |     | -97  | dBm    |

|                         | For f:<br>f <sub>c</sub> +1MHz>f>f <sub>c</sub> +880kHz<br>f <sub>c</sub> -880kHz>f>f <sub>c</sub> -1MHz   |      |     | -72  | dBm    |

| Allowed Phase noise     | f=1Hz                                                                                                      |      |     | -24  | dBc/Hz |

|                         | 10kHz>f>100Hz                                                                                              |      |     | -90  | dBc/Hz |

#### 2.2.1 b) Argos4

| PARAMETER               | CONDITIONS  | 6            | MIN | TYP | MAX  | UNIT   |

|-------------------------|-------------|--------------|-----|-----|------|--------|

| Input power level       | Tj = 25°C   | Tj = 25°C    |     |     | -112 | dB     |

| Noise figure            | Tj = 25°C   |              |     |     | 5.8  | dB     |

| ADC resolution          |             |              |     | 5   |      | Bits   |

| ADC sampling frequency  |             |              |     | 2   |      | MHz    |

| Demodulator loss        |             |              |     |     | 2    | dB     |

| Allowed spurious levels | In-band     | In-band      |     |     | -145 | dBm    |

|                         | Out-of-band | 1MHz offset  |     |     | -97  | dBm    |

|                         |             | 2MHz offset  |     |     | -92  | dBm    |

|                         |             | 5MHz offset  |     |     | -77  | dBm    |

|                         |             | 10MHz offset |     |     | -67  | dBm    |

| Allowed Phase noise     | f=1Hz       |              |     |     | -24  | dBc/Hz |

|                         | 10kHz>f>100 | Hz           |     |     | -90  | dBc/Hz |

#### 2.2.2 Transmitter

#### 2.2.2 a) General characteristics

| <ul><li>2.2.2 Transmitter</li><li>2.2.2 a) General character</li></ul> | eristics   |     |      |     |        |

|------------------------------------------------------------------------|------------|-----|------|-----|--------|

| PARAMETER                                                              | CONDITIONS | MIN | TYP  | MAX | UNIT   |

| TX output power                                                        |            |     | 1    |     | mW     |

| SSB phase noise                                                        | 100Hz      |     | -83  |     | dBc/Hz |

|                                                                        | 1kHz       |     | -91  |     | dBc/Hz |

|                                                                        | 10kHz      |     | -94  |     | dBc/Hz |

|                                                                        | 100kHz     |     | -95  |     | dBc/Hz |

|                                                                        | 1MHz       |     | -124 |     | dBc/Hz |

| Phase accuracy                                                         |            |     | 1.06 |     | Deg.   |

| Amplitude accuracy                                                     |            |     | 0.3  |     | dB     |

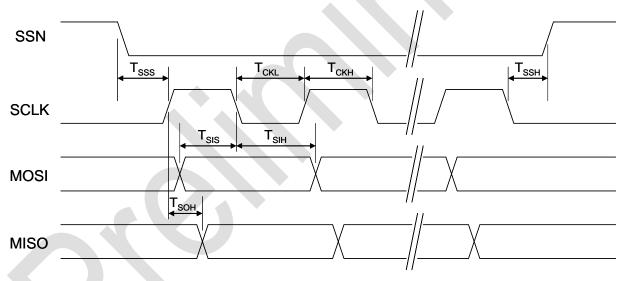

### 2.3 SPI Interface

This is the interface between the MCU and the ARTIC. The SPI interface makes use of the standard generic ANSEM SPI interface, which is a 4-wire interface (SCLK, SSN, MOSI, and MISO). Its behaviour is quasi real time meaning that during accesses the provided/requested data word is been processed by the embedded DSP before the next word arrives/is requested.

Following SPI modes are implemented in the ARTIC: standard access mode, burst mode and command mode.

| PARAMETER        | DESCRIPTION                     | MIN | MAX | UNIT |

|------------------|---------------------------------|-----|-----|------|

| Тскн             | SCLK high time                  | 20  | -   | ns   |

| ТСКГ             | SCLK low time                   | 20  |     | ns   |

| T <sub>SSS</sub> | SSN falling to first SCLK edge  | 20  | -   | ns   |

| T <sub>SSH</sub> | Last SCLK edge to SSN rising    | 20  |     | ns   |

| T <sub>SIS</sub> | MOSI valid to SCLK sample edge  | 10  |     | ns   |

| T <sub>SIH</sub> | SCLK sample edge to MOSI change | 10  | -   | ns   |

| T <sub>SOH</sub> | SCLK shift edge to MISO change  |     | 10  | ns   |

#### 2.3.1 SPI Timing Characteristics

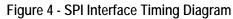

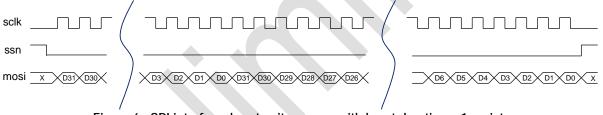

#### 2.3.2 Standard mode

In the standard mode the protocol first sends an address (7 b), followed by an opcode bit (indicating read or write), and finally the data (24 b, send by master or slave, depends on the opcode bit). See Figure 5.

Opcode bit:

- Read : 1

- Write : 0

Figure 5 - SPI Interface Communication Protocol

The registers that can be accessed using the standard access mode are listed in Table 1. Their usage is explained further on.

| address | R/W  | Name          |

|---------|------|---------------|

| 0x00    | W    | BURSTMODE_REG |

| 0x01    | RW/R |               |

#### *2.3.2 a)* BURSTMODE\_REG

Table 2 - BURSTMODE register

| R/W                           | Reset    | Bit 23                | Bit 22 | Bit 21 | Bit 20            | Bit 19             | Bit 18 | Bit 17              | Bit 16 |

|-------------------------------|----------|-----------------------|--------|--------|-------------------|--------------------|--------|---------------------|--------|

|                               | 0000000  | reserved              |        |        | burst_mode<br>_on | burst_mem_sel<1:0> |        | burst_r_nw<br>_mode |        |

|                               | Reset    | Bit 15                | Bit 14 | Bit 13 | Bit 12            | Bit 11             | Bit 10 | Bit 9               | Bit 8  |

| W                             | 00000000 | burst_start_add<15:8> |        |        |                   |                    |        |                     |        |

|                               | Reset    | Bit 7                 | Bit 6  | Bit 5  | Bit 4             | Bit 3              | Bit 2  | Bit 1               | Bit 0  |

| 00000000 burst_start_add<7:0> |          |                       |        |        |                   |                    |        |                     |        |

| Bit 19    | burst_mode_on         | '1', the next SPI access is considered a burst access.                          |

|-----------|-----------------------|---------------------------------------------------------------------------------|

| Bit 18:17 | burst_mem_sel<1:0>    | Selects which memory is accessed by the SPI burst.                              |

|           |                       | "00" : Program memory                                                           |

|           |                       | "01" : X memory                                                                 |

|           |                       | "10" : Y memory                                                                 |

|           |                       | "11" : I/O memory.                                                              |

| Bit 16    | burst_r_nw_mode       | Indicates if the SPI burst is a read or a write burst.                          |

|           |                       | '0' : write burst                                                               |

|           |                       | '1' : read burst.                                                               |

| Bit 15:0  | burst_start_add<15:0> | Indicates the location of the register that is first accessed by the SPI burst. |

|           |                       | , , , , , , , , , , , , , , , , , , ,                                           |

#### 2.3.3 Burst mode

The default SPI protocol is extended with an extra feature: burst mode (for both read and write actions). The burst mode allows access to the memory regions used by the DSP and can be used to transfer large amounts of data.

A burst mode is configured by performing a standard mode write to the dedicated 'burst mode' register, followed by the actual burst. The SSN line must be released briefly after the 'burst mode' register is written to allow the ARTIC to configure for the burst. The next time the SSN goes low the actual burst starts.

See Table 2 for the content of the burst mode register. This register is not used for any other purpose then to control burst mode, and is write only.

The data width used during burst mode is automatically selected, based on the selected memory section. X, Y and shared IO memory use 24 bits. Program memory P uses 32 bits. See 2.4 for more information about the ARTIC memories.

#### 2.3.3 a) Write

During a burst write access, the first 24/32 bits received via the MOSI line are written to the register at the address as specified by burst\_start\_add<15:0>. Next the internal address pointer is incremented by 1. The next 24/32 bits are written to this new address location (=burst\_start\_address+ 1). Next the internal address pointer is again incremented by 1. This mechanism continues during the complete duration of the burst.

The data is sent or received MSBit first. The SSN line needs to remain active low during the complete duration of the burst, since a rising edge on the SSN line is used to indicate the end of the burst. In this event, the next SPI access will be treated again as a standard access. In order to perform another burst access, first bit 'burst\_mode\_on in register 'burst mode' must be written again.

Figure 6 - SPI interface, burst write access with burst duration = 1 register

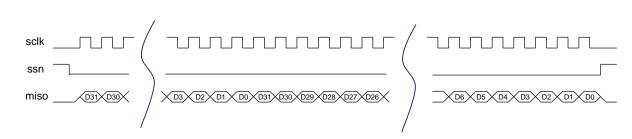

#### 2.3.3 b) Read

During a burst read access, the 24/32 bit content of the register at the address as specified by 'burst\_start\_add<15:0>' is output via the MISO line (MSBit first).

The user has to wait for the duration of 24 SPI clock cycles after configuring the burst read mode, before starting the first read. This allows some time for the internal memory access block to retrieve the first data sample.

A next read is triggered when the previous read data starts to be shifted out by the SPI interface. The address is incremented automatically, as is the case during a write burst.

The SSN line needs to remain active low during the complete duration of the burst. A rising edge on the SSN line indicates the end of a burst. In this event, the next SPI access is treated again as a standard access.

The data during a burst is sent or received MSBit first (like it is the case during a normal access).

Figure 7 - SPI interface, burst read access with burst duration = 1 register

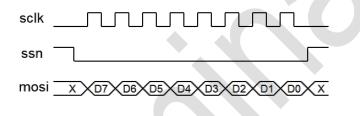

#### 2.3.4 Command access

The SPI protocol is extended with a second feature: command access. A command access exists of a short SPI access of only 8 clock cycles. If the SSN line goes inactive after 8 clock cycles, the ARTIC will interpret the 8-bit as a command access, see Figure 8. With this feature, 256 different commands can be sent directly to the DSP, see section 3.3 for a complete list of commands.

In case the ARTIC is up and running, one of the 2 interrupts lines will be set when the command has been processed by the DSP. For each interrupt line that is set, additional information can be accessed as described in 3.2.

Figure 8 - SPI 8-bit command access

### 2.4 ARTIC Memories

The ARTIC has 4 types of memory which can only be accessed using the SPI burst mode. The maximum speed at which the SPI can operate depends on the memory that is accessed. See Table 3 for a description.

| Memory | Word<br>size | Memory<br>size | Max SPI clock<br>speed[MHz] |       | Description        |

|--------|--------------|----------------|-----------------------------|-------|--------------------|

|        |              | [words]        | Read                        | Write |                    |

| Р      | 32 bit       | 10240          | 1.5                         | 5     | DSP Program memory |

| Х      | 24 bit       | 21845          | 1.25                        | 3.5   | DSP X memory       |

| Y      | 24 bit       | 6826           | 1.25                        | 3.5   | DSP Y memory       |

| 10     | 24 bit       | -              | 1.25                        | 3.5   | ARTIC IO memory    |

Table 3 - ARTIC memory widths

The P, X and Y memories must be loaded each time after reset. Only firmware that is supplied by ANSEM can be used. Using other software will void all warranties immediately.

The firmware can be loaded by the MCU or the ARTIC can automatically download firmware from an external memory. See 3.1

### 2.5 Boot configuration

The ARTIC can boot the firmware from an external flash or the user can supply the firmware via SPI. The ARTIC will boot from the [onboard] external flash memory when the boot pin is high and reset is released. If the boot pin is held low at reset the ARTIC will wait for the MCU to upload the Firmware. The boot pin must be connected either through GND or VCC using a pulldown or pullup resistor.

### 2.6 Bias

Use a  $33k\Omega$  1% tolerance resistor as bias reference for the ARTIC. [pin 41]. This resistor is used to generate all internal reference currents.

### 2.7 Reset

The reset is active low [pin 1]. Use a  $100k\Omega$  pullup resistor to activate the ARTIC at power-up.

### 2.8 GPIO

The ARTIC has 8 GPIO's available. Currently only GPIO7 is used as an output to activate an external PA during transmission.

### 2.9 Flash interface

A Flash memory can be attached to store the ARTIC firmware. The ARTIC is able to boot from the flash memory. See section 3.1.1 how this boot method is accessed. The external flash memory is connected to the ARTIC through a dedicated SPI interface, which f.i. can be found on the SST25VF020B from Microchip.

### 2.10 TCXO interface

The ARTIC uses a 26MHz TCXO. The stability of the TCXO is crucial to meet the ARGOS requirements. All tests were performed using the KT1612AWC26000. The TCXO is only activated during transmission or reception in order to save power. The rest of the time an internal oscillator running at 500 kHz is used.

# 3. Operating the device

This chapter covers the operating instructions of the ARTIC chip:

- Start-up and Boot process.

- Reading the ARTIC status

- Controlling the ARTIC.

- Transmit and receive messages.

### 3.1 Start-up sequence

The ARTIC requires firmware to be loaded after each power up or reset. The firmware can be uploaded by SPI or using an external flash memory. Both options are described in this paragraph.

#### 3.1.1 Flash memory

To boot the ARTIC chip from the attached flash memory the following actions have to be made:

- 1. Apply the 3.3V and 1.8V supplies of the ARTIC chip.

- 2. Pull the BOOT pin to 3.3V

- 3. Pull the RESETB pin to 3.3V

The ARTIC will read the external flash memory and starts booting. Interrupt 2 (INT 2) will be set

4. Wait until INT1 pin is high. [2.25 sec]

The ARTIC chip is ready to accept commands.

#### 3.1.2 SPI booting

Following actions have to be made to boot the ARTIC chip by transferring the program over SPI:

- 1. Apply the 3.3V and 1.8V supplies of the ARTIC chip.

- 2. Pull the BOOT pin to 0V

- 3. Pull the RESETB pin to 3.3V

The ARTIC is brought out of reset. Interrupt 2 (INT 2) will be set

- 4. Write the DSP program memory using SPI

- a. Write to the top register *burstmode\_reg* with following information:

- i. Memory type: program memory (00b)

- ii. Address range (0b)

- iii. write mode (0b)

- The 32b sequence written via SPI will be 0x00080000

- b. Next in a SPI burst mode the data is written to the program memory

- 5. Write the DSP X memory using SPI

- a. Write to the top register *burstmode\_reg* with following information:

- i. Memory type: X data memory (01b)

- ii. Address range (0d)

- iii. write mode (0b)

- The 32b sequence written via SPI will be 0x000A0000

- b. Next in a SPI burst mode the data is written to the Y memory

- 6. Write the DSP Y memory using SPI

- a. Write to the top register *burstmode\_reg* with following information:

- i. Memory type: Y data memory (10b)

- ii. Address range (0d)

- iii. write mode (0b)

- The 32b sequence written via SPI will be 0x000C0000

- b. Next in a SPI burst mode the data is written to the Y memory

- Perform one 24 bit write access to the top level *register* dsp\_ctrl\_reg to activate the DSP.

i. The 32b sequence written via SPI will be 0x02000000

The ARTIC will start booting.

8. Wait until INT1 pin is high. [250msec]

The ARTIC chip is ready to accept commands.

Note:

- Step 1 and 2 may be concurrent by connecting the RESETB pin on the PCB to the 3.3V supply.

- During the booting process CRC's are calculated, see 0.

## 3.2 Firmware status – interrupt flags

The ARTIC firmware will talk to the MCU using 2 interrupt lines (INT1, INT2) and a number of internal flags. These flags provide more insight why a specific interrupt is set. The firmware state can also be consulted.

The user can access the firmware status/interrupt flags by reading a single register. This 24-bit register is present in the IO memory at address 0x8018 and can be accessed using an SPI burst. This register can only be read.

The complete 32-bit sequence is 0x000F8018. Next in a 24-bit SPI burst the register is read.

| Table 4 - Firmware status | s - interrupt flags |

|---------------------------|---------------------|

|---------------------------|---------------------|

| BI<br>T | Signal                  |                      | Description                                          |

|---------|-------------------------|----------------------|------------------------------------------------------|

| 0       | IDLE                    | Current<br>Firmware  | The firmware is idle and ready to accept commands.   |

| 1       | RX_IN_PROGRESS          | state                | The firmware is receiving.                           |

| 2       | TX_IN_PROGRESS          |                      | The firmware is transmitting.                        |

| 3       | BUSY                    |                      | The firmware is changing state.                      |

| 4       | RX_VALID_MESSAGE        | Interrupt            | A message has been received.                         |

| 5       | RX_SATELLITE_DETECTED   | 1 flags              | A satellite has been detected.                       |

| 6       | TX_FINISHED             |                      | The transmission was completed.                      |

| 7       | MCU_COMMAND_ACCEPTED    |                      | The configuration command has been accepted.         |

| 8       | CRC_CALCULATED          |                      | CRC calculation has finished.                        |

| 9       | IDLE_STATE              |                      | Firmware returned to the idle state.                 |

| 10      | RX_CALIBRATION_FINISHED |                      | RX offset calibration has completed.                 |

| 11      | -                       |                      | -                                                    |

| 12      | -                       |                      | -                                                    |

| 13      | RX_TIMEOUT              | Interrupt<br>2 flags | The specified reception time has been exceeded.      |

| 14      | SATELLITE_TIMEOUT       |                      | No satellite was detected within the specified time. |

| 15      | RX_BUFFER_OVERFLOW      |                      | A received message is lost. No buffer space left.    |

| 16      | TX_INVALID_MESSAGE      |                      | Incorrect TX payload length specified.               |

| 17      | MCU_COMMAND_REJECTED    |                      | Incorrect command send or Firmware is not in idle.   |

| 18      | MCU_COMMAND_OVERFLOW    |                      | Previous command was not yet processed.              |

| 19      | -                       |                      | •                                                    |

| 20      | -                       |                      | •                                                    |

| 21      | INTERNAL_ERROR          |                      | An internal error has occurred.                      |

| 22      | dsp2mcu_int1            |                      | Interrupt 1 pin status                               |

| 23      | dsp2mcu_int2            |                      | Interrupt 2 pin status                               |

### 3.3 MCU commands

If the user transfers only 8 bit over SPI (indicated by SSN going high after 8 bits), the data is interpreted as a command. The list of available commands is separated into 3 sets:

- Configuration

- Instructions

- Housekeeping

#### Note:

These commands are handled by the DSP and can require some time to be processed. The DSP does not buffer these commands. If a previous command is not completed, the ARTIC will set interrupt 2 with the MCU\_COMMAND\_OVERFLOW flag. This second command is lost.

#### 3.3.1 Configuration

The following commands are available supporting all ARGOS 2/3/4 standards. The user should check which commands are supported by the firmware as specified in the README file.

These commands will configure the DSP into the correct ARGOS mode. If the command is processed, the DSP will respond by setting INT 1 high and by stating MCU\_COMMAND\_ACCEPTED as described in 3.2.

The ARTIC will reject configuration commands send during reception or transmission. If a command is rejected INT 2 will be set with the MCU\_COMMAND\_REJECTED flag.

If an unsupported command is send, INT 2 will also be set with the MCU\_COMMAND\_REJECTED flag.

| 8 bit<br>command | Configuration command         | Description                                   |

|------------------|-------------------------------|-----------------------------------------------|

| commanu          |                               |                                               |

| 0000001b         | Set ARGOS 4 RX mode           | Configure the receiver in ARGOS 4 mode        |

| 00000010b        | Set ARGOS 3 RX mode           | Configure the receiver in ARGOS 3 mode        |

| 00000011b        | Set ARGOS 3 RX backup mode    | Configure the receiver in ARGOS 3 backup mode |

| 00000100b        | Set PTT-A2 TX mode            | Configure the transmitter in ARGOS 2 mode     |

| 00000101b        | Set PTT-A3 TX mode            | Configure the transmitter in ARGOS 3 mode     |

| 00000110b        | Set PTT-ZE TX mode            | Configure the transmitter in ARGOS ZE mode    |

| 00000111b        | Set ARGOS 3 PTT-HD TX mode    | Configure the transmitter in ARGOS 3-HD mode  |

| 00001000b        | Set ARGOS 4 PTT-HD TX<br>mode | Configure the transmitter in ARGOS 4-HD mode  |

| 00001001b        | Set ARGOS 4 PTT-MD TX<br>mode | Configure the transmitter in ARGOS 4-MD mode  |

| 00001010b        | Set ARGOS 4 PTT-VLD TX mode   | Configure the transmitter in ARGOS 4-VLD mode |

#### Table 5 - Configuration commands

When an ARGOS 4 transmission command is used, the receiver will be automatically configured for ARGOS 4. Equally, using an ARGOS 3 transmission command will configure the receiver in ARGOS 3.

#### *3.3.1 a)* Verify configuration

The configuration of the ARTIC can be verified by reading the 'ARGOS configuration' register. The content of this register is explained in Table 6.

See 3.4 for how to access the 'ARGOS configuration' register. This register is read only.

| R/W | Reset    | Bit 23           | Bit 22   | Bit 21 | Bit 20 | Bit 19  | Bit 18   | Bit 17 | Bit 16 |  |

|-----|----------|------------------|----------|--------|--------|---------|----------|--------|--------|--|

|     | 00000000 |                  | reserved |        |        |         |          |        |        |  |

|     | Reset    | Bit 15           | Bit 14   | Bit 13 | Bit 12 | Bit 11  | Bit 10   | Bit 9  | Bit 8  |  |

| R   | 00000000 | reserved         |          |        |        |         |          |        |        |  |

|     | Reset    | Bit 7            | Bit 6    | Bit 5  | Bit 4  | Bit 3   | Bit 2    | Bit 1  | Bit 0  |  |

|     | 00010000 | RX configuration |          |        |        | TX conf | guration |        |        |  |

### Table 6 - ARGOS configuration register

#### Bit 7-4 RX configuration

- 0x0 : ARGOS 3 RX [default]

- 0x1 : ARGOS 3 RX backup mode

- 0x2 : ARGOS 4 RX

#### Bit 3-0 TX configuration

- 0x0 : ARGOS PTT-A2 [default]

- 0x1 : ARGOS PTT-A3

- 0x2 : ARGOS PTT-ZE

- 0x3 : ARGOS PTT-HD

- 0x4 : ARGOS PTT-A4-MD

- 0x5 : ARGOS PTT-A4-HD

- 0x6 : ARGOS PTT-A4-VLD

#### 3.3.2 Instructions

The commands in Table 7 are used to start receiving or to transmit a message. Each command is explained separately alongside a list of all the possible interrupt flags that can be set during the execution.

| 8 bit command | Instruction command                                |  |  |  |  |

|---------------|----------------------------------------------------|--|--|--|--|

| 01000001b     | Start continuous reception                         |  |  |  |  |

| 01000010b     | Start receiving 1 message                          |  |  |  |  |

| 01000011b     | Start receiving 2 messages                         |  |  |  |  |

| 01000110b     | Start reception for fixed time                     |  |  |  |  |

| 01001000b     | Transmit one package and go to idle                |  |  |  |  |

| 01001001b     | Transmit one package and start reception for fixed |  |  |  |  |

|               | time                                               |  |  |  |  |

| 01010000b     | Go to idle                                         |  |  |  |  |

| 01010101b     | Satellite detection                                |  |  |  |  |

Table 7 - Instruction commands

Note:

• Both interrupts and all interrupt flags will be cleared automatically whenever an instruction command is send.

#### *3.3.2 a)* Start continuous reception

Start the ARTIC in receiving mode for an unlimited time and unlimited number of messages. The user has to use the 'Go to idle' command to stop the receiver. See 3.6.2 for the interrupt explanation.

| Possible interrupt flags | Interrupt |

|--------------------------|-----------|

| RX_VALID_MESSAGE         | 1         |

| RX_BUFFER_OVERFLOW       | 2         |

| RX_SATELLITE_DETECTED    | -         |

#### *3.3.2 b)* Start receiving 1 message

Start the ARTIC in receiving mode for an unlimited time until 1 message has been received. If the message is received the Artic will go to IDLE. The user can abort the reception using the 'Go to idle' command. See 3.6.2 for the interrupt explanation.

| Possible interrupt flags | Interrupt |

|--------------------------|-----------|

| RX_VALID_MESSAGE         | 1         |

| RX_SATELLITE_DETECTED    | -         |

#### *3.3.2 c)* Start receiving 2 messages

Start the ARTIC in receiving mode for an unlimited time until 2 messages have been received. If the 2 messages are received the ARTIC will go to IDLE. The user can abort the reception using the 'Go to idle' command. See 3.6.2 for the interrupt explanation.

| Possible interrupt flags           | Interrupt |

|------------------------------------|-----------|

| RX_VALID_MESSAGE                   | 1         |

| RX_SATELLITE_DETECTED <sup>2</sup> | -         |

### 3.3.2 d) Start reception for fixed time

Start the ARTIC in receiving mode for a programmable time and for an unlimited amount of messages. After the programmed time has finished the ARTIC will go to IDLE. The user can abort the reception using the 'Go to idle' command. After the receiver has been active for the programmed amount of time, INT 2 will be set with the 'RX\_TIMEOUT' flag. See 3.6.2 for the explanation of the other interrupts. See 3.6.4 on how to configure the timeout.

| Possible interrupt flags           | Interrupt |

|------------------------------------|-----------|

| RX_VALID_MESSAGE                   | 1         |

| IDLE_STATE                         | 1         |

| RX_TIMEOUT                         | 2         |

| RX_BUFFER_OVERFLOW                 | 2         |

| RX_SATELLITE_DETECTED <sup>2</sup> | -         |

<sup>&</sup>lt;sup>2</sup> During reception the RX\_SATELLITE\_DETECTED' flag will be set high as long as the ARTIC is receiving 0x7E flags.

#### 3.3.2 e) Transmit one package and go to idle

The ARTIC will transmit the payload message according to the configured ARGOS mode and will go to IDLE. See 3.4.1 for more information

| Possible interrupt flags | Interrupt |

|--------------------------|-----------|

| TX_FINISHED              | 1         |

| IDLE_STATE               | 1         |

| TX_INVALID_MESSAGE       | 2         |

#### 3.3.2 f) Transmit one package and start reception for fixed time

The ARTIC will transmit the payload message according to the configured ARGOS mode and will switch to reception mode as described in '*Start reception for fixed time*'. See 3.4.1 for more information about the transmission.

| Possible interrupt flags Interru   |   |

|------------------------------------|---|

| TX_FINISHED                        | 1 |

| RX_VALID_MESSAGE                   | 1 |

| RX_TIMEOUT                         | 2 |

| RX_BUFFER_OVERFLOW                 | 2 |

| TX_INVALID_MESSAGE                 | 2 |

| RX_SATELLITE_DETECTED <sup>3</sup> | - |

#### 3.3.2 g) Go to idle

The ARTIC will return to idle mode. This command will not have an effect whenever the ARTIC is in 'BUSY' state. Once the ARTIC has returned to the idle state, interrupt 1 will be raised and the IDLE\_STATE flag will be set.

| Possible interrupt flags | Interrupt |

|--------------------------|-----------|

| IDLE_STATE               | 1         |

#### *3.3.2 h)* Satellite detection

The ARTIC will start looking for a satellite for a specified amount of time. If no satellite is detected, INT 2 will be set with the 'SATELLITE\_TIMEOUT' flag. If a satellite was detected, by receiving 5 consecutive 0x7E flags, INT 1 will be set with the 'RX\_SATELLITE\_DETECTED' flag. See 3.6.4 on how to configure the timeout.

| Possible interrupt flags           | Interrupt |

|------------------------------------|-----------|

| RX_SATELLITE_DETECTED <sup>2</sup> | 1         |

| SATELLITE_TIMEOUT                  | 2         |

#### 3.3.3 Housekeeping

Following commands can be used to clear the interrupt and the corresponding flags. The ARTIC chip will not re-raise an interrupt before it is cleared by the MCU. Henceforth it is good practice to clear an interrupt once is has been set.

<sup>&</sup>lt;sup>3</sup> During reception the 'RX\_SATELLITE\_DETECTED' flag will be set high as long as the ARTIC is receiving 0x7E flags.

| 8 bit command<br>word | housekeeping<br>commands |

|-----------------------|--------------------------|

| 10XXXXXXb             | Clear interrupt line 1   |

| 11XXXXXXb             | Clear interrupt line 2   |

### 3.4 Memory locations

Table 8 is a list of the memory locations that are needed to configure the Firmware. All these parameters are located in the X memory and must be accessed using the burst mode as described in 2.3.3.

| Parameter name             | Start address [hex] | Size [24-bit<br>words] | Read /<br>Write |

|----------------------------|---------------------|------------------------|-----------------|

| ARGOS configuration        | 0x0384              | 1                      | R               |

| RX payload                 | 0x0200              | 9                      | R               |

| RX filtering configuration | 0x0209              | 104                    | R/W             |

| RX timeout                 | 0x0271              | 1                      | R/W             |

| Satellite detection        | 0x0272              | 1                      | R/W             |

| timeout                    |                     |                        |                 |

| TX payload                 | 0x0273              | 220                    | W               |

| TX frequency Argos 2/3     | 0x034F              | 1                      | R/W             |

| TX frequency Argos 4       | 0x035F              | 1                      | R/W             |

| TCXO warmup time           | 0x036F              | 1                      | R/W             |

| TCXO control               | 0x0370              | 1                      | R/W             |

| CRC results                | 0x0371              | 3                      | R               |

| TX certification interval  | 0x0379              | 1                      | R/W             |

#### 3.4.1 Read example

Read the 'CRC results' at address 0x0371, length: 3-words

- 1. Configure SPI burst to read X memory at address 0x0371 SPI Write 0x000B0371 [32-bit]

- 2. Read the CRC results SPI read 0x000000 0x000000 [3x 24-bit]

The SSN line must be raised briefly between step 1 and 2. See 0 for more information about the CRC check.

### 3.4.2 Write example

Write the 'RX timeout' parameter at address 0x0271 with value 0x00000A [ = 10 seconds timeout]

- 3. Configure SPI burst to write X memory at address 0x0271

- SPI Write 0x000A0271 [32-bit] 4. Write the 24-bit parameter

- SPI write **0x00000A** [24-bit]

The SSN line must be raised briefly between step1 and 2.

### 3.5 Transmission

The ARTIC is able to transmit messages according the various ARGOS modulation standards. See 3.3.1 on how to configure the ARTIC. Only 1 transmission will occur for each TX command.

#### 3.5.1 Transmission payload

Depending on the configured ARGOS mode different message lengths can be transmitted. The user has to ensure that the message makes sense to the satellite. The ARTIC only checks the maximum allowed message length.

Some ARGOS transmission standards require specific bits to be added for correct reception by the satellite. For each standard a brief overview is given. Please read the ARGOS transmission standard specifications to comprehend the message content thoroughly.

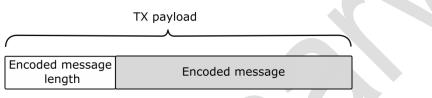

The transmission payload must be written before any transmission command is issued.

The payload buffer contains 2 items:

- Encoded message length:

- Defines the length of the TX user message in bits.

- This user message length occupies the first 24-bit word of the TX payload.

- Encoded message

- This is the encoded message as described in

- o Starts at the second 24-bit word of the TX payload.

- The first bit of the Uplink message is aligned with the MSB of the second 24-bit word of the payload buffer. Bit 25 of the Uplink message is aligned with the MSB of the third 24-bit word of the payload buffer. In this way the total Uplink message occupies a number of consecutive 24-bit words in the payload buffer.

- In case the total length of the Uplink message is not a multiple of 24 bits, the last used 24-bit word of the payload buffer should be stuffed by the MCU with 0's at the LSB locations.

Note that if the TX payload is smaller than the TX payload buffer (220 x 24 bit words), the not used words at the end of the buffer don't need to be written by the MCU.

The location of the TX payload can be found in Table 8.

Following tables explain the uplink message composition according to the different ARGOS standards.

### 3.5.1 a) ARGOS 2

| Message length<br>[bits] | ID number [bits] | User data [bits] |

|--------------------------|------------------|------------------|

| 4                        | 28               | 24               |

|                          |                  | 56               |

|                          |                  | 88               |

|                          |                  | 120              |

|                          |                  | 152              |

|                          |                  | 184              |

|                          |                  | 216              |

|                          |                  | 248              |

### Table 9 - ARGOS 2 uplink messages

#### 3.5.1 b) ARGOS 3

| Message length [bits] | ID number<br>[bits] | User data<br>[bits] | Tail bits [bits] |

|-----------------------|---------------------|---------------------|------------------|

| 4                     | 28                  | 24                  | 7                |

|                       |                     | 56                  | 8                |

|                       |                     | 88                  | 9                |

|                       |                     | 120                 | 7                |

|                       |                     | 152                 | 8                |

|                       |                     | 184                 | 9                |

|                       |                     | 216                 | 7                |

|                       |                     | 248                 | 8                |

### Table 10 - ARGOS 3 uplink messages

#### 3.5.1 c) ARGOS ZE

Table 11 - ARGOS ZE uplink message

| Message length [bits] | ID number [bits] | Tail bits [bits] |

|-----------------------|------------------|------------------|

| 0                     | 28               | 8                |

#### 3.5.1 d) ARGOS 3-HD

Table 12 - ARGOS 3 HD uplink messages

| ID number<br>[bits] | User data [bits] | Tail bits [bits]                                                                  |

|---------------------|------------------|-----------------------------------------------------------------------------------|

| 28                  | 32               | 8                                                                                 |

|                     | 512              | 8                                                                                 |

|                     | 1024             | 9                                                                                 |

|                     | 1536             | 7                                                                                 |

|                     | 2048             | 8                                                                                 |

|                     | 2560             | 9                                                                                 |

|                     | 3072             | 7                                                                                 |

|                     | 3584             | 8                                                                                 |

|                     | 4096             | 9                                                                                 |

|                     | 4608             | 7                                                                                 |

|                     | [bits]           | [bits]<br>28<br>32<br>512<br>1024<br>1536<br>2048<br>2560<br>3072<br>3584<br>4096 |

#### 3.5.1 e) ARGOS 4 MD

The message length is coded inside the synchronization pattern which is added by the ARTIC. After each block of 512 bits the MCU has to add 1 parity bit and 2 tail bits. The Frame check sequence is only used during PMT mode and can be used for additional data in PTT mode. For more details read the document A4-SS-TER-SP-0078-CNS.

| ID number<br>[bits] | User data [bits] | Frame check sequence<br>[bits] |

|---------------------|------------------|--------------------------------|

| 28                  | 452              | 32                             |

|                     | 964              |                                |

Table 13 - ARGOS4 MD uplink messages

#### 3.5.1 f) ARGOS 4 HD

The message length is coded inside the synchronization pattern which is added by the ARTIC. For each block of 1024 bits the MCU has to add 1 parity bit and 2 tail bits. The Frame check sequence is only used during PMT mode and can be used for additional data in PTT mode. For more details read the document A4-SS-TER-SP-0078-CNS.

| Table 14 - ARGOS 4 HD uplink message | essages | ıplink n | 4 HD | ARGOS | Table 14 |

|--------------------------------------|---------|----------|------|-------|----------|

|--------------------------------------|---------|----------|------|-------|----------|

| ID number<br>[bits] | User data<br>[bits] | Frame check sequence [bits] |

|---------------------|---------------------|-----------------------------|

| 28                  | 964                 | 32                          |

|                     | 1988                |                             |

|                     | 3012                |                             |

|                     | 4036                |                             |

|                     | 5060                |                             |

### 3.5.1 g) ARGOS 4 VLD

The message length is coded inside the synchronization pattern which is added by the ARTIC.

| Table 15 - | ARGOS 4 | VLD upli | nk messages |

|------------|---------|----------|-------------|

|            |         |          | , U         |

| ID number<br>[bits] | User data<br>[bits] |

|---------------------|---------------------|

| 28                  | 0                   |

|                     | 28                  |

#### 3.5.2 TCXO warm up time

Some TCXO's require a warmup time before each transmission in order to stabilize the frequency and to meet the certification requirements. This warm up time is set by default to 10 seconds but can be altered if another TCXO is used. The TCXO warmup time will start after sending a TX instruction command. During this time the ARTIC will appear in BUSY mode. See 3.4 for the 'TCXO warmup' memory location. If the warmup time is set to 0, no frequency stabilization is performed.

| Parameter        | Unit    | Default |

|------------------|---------|---------|

| TCXO warmup time | Seconds | 10      |

#### 3.5.3 Transmission frequency

Before transmitting the TX frequency should be set by the MCU. The ARTIC uses separate transmission frequency parameters for ARGOS 2/3 and ARGOS 4, the frequency can be adjusted up to a few Hz.

In order to change the transmission frequency, the fractional PLL parameter has to be calculated as follows:

factional part = round

$$\left(2^{22} * \left(\frac{(tx_{freq} * 4)}{26e6} - 61\right)\right)$$

Example for 401.65MHz:

fractional part = round

$$\left(2^{22} * \left(\frac{(401.65e6 * 4)}{26e6} - 61\right)\right) = 3323179 = 0x32b52b$$

This fractional number must be written in the 'TX frequency ARGOS x' memory locations as specified in 3.4.

Transmission frequency shall be chosen adequately, and follow the frequency allocation defined by Kinéis.

### 3.6 Reception

The ARTIC can buffer 2 messages internally and can be programmed to filter messages based upon their ID. The CRC of each received message can be automatically verified.

#### 3.6.1 Configuring the downlink message filtering

The downlink message filtering can be configured by the MCU via the X data memory. See 0 for the 'RX filtering configuration' parameter for the memory location. First the address map is shown, next the features are explained.

| Address<br>offset | Content                            | Reset    |

|-------------------|------------------------------------|----------|

| 0                 | EnableCRC                          | 0x000001 |

| 1                 | TransparentMode                    | 0x000000 |

| 2                 | Not used                           | -        |

| 3                 | Length of address LUT              | 0x000000 |

| 4                 | Address LUT – ID number 1, LSBits  | -        |

| 5                 | Address LUT – ID number 1, MSBits  | -        |

| 6                 | Address LUT – ID number 2, LSBits  | -        |

| 7                 | Address LUT – ID number 2, MSBits  | -        |

|                   |                                    |          |

| 104               | Address LUT – ID number 50, LSBits | -        |

| 105               | Address LUT – ID number 50, MSBits | -        |

Table 16 - Downlink message filtering memory map

#### EnableCRC:

Each downlink message contains a CRC field. During normal operation only messages with a valid CRC are passed to the MCU.

- If set to 0x000001, the CRC check is enabled. [Default]

- If set to 0x000000, the CRC check is disabled. All received messages are considered valid.

#### TransparentMode.

In the default situation only messages with an ID mentioned in the Address LUT are sent to the MCU. This filtering can be bypassed by activating the transparent mode.

- If set to 0x000001, the transparent mode is enabled. All messages are send to the MCU.

- If set to 0x000000, the filtered mode is enabled. [Default]

#### Length of address LUT

- This word determines the length of the Address LUT.

- The max length is 50

#### Address LUT

- The Address LUT lists all the ID numbers that should be compared against the addressee Identification field of an incoming message during filtered mode, in order to determine if the incoming message should be signalled to the MCU via INT1.

- Since an ID number is 28 bits long, it is spread over 2 consecutive LUT words.

- The 24 LSBits are stored at the lowest address.

- The 4 MSBits are stored at the highest address, using format 0x00000Y, with Y = 4 MSBits.

- The content of each 28 bit ID number can be anything, but to be compliant to the ARGOS standards, it should be one of the following

- Unique Node ID number as assigned by CLS

- Group ID of group(s) to which the PMT belongs.

- o All cast ID supported by the PMT

#### 3.6.2 Reception signalling and buffering

The ARTIC can buffer 2 messages internally before the third message arrives, then this third message will be discarded. On this event INT 2 will be set with the RX\_BUFFER\_OVERFLOW flag.

When the ARTIC receives a valid downlink message, it raises INT 1 with the RX\_VALID\_MESSAGE flag. The MCU can then use an SPI burst access to read the downlink message from the X data memory.

After reading the downlink message, the ARTIC reception buffer must be cleared. This is done by sending the 'Clear interrupt 1' command.

If a second message was received it will be moved to the 'RX payload' buffer upon the 'Clear interrupt 1' command. In this case INT 1 will be re-raised after 100usec. The MCU can read the RX payload again and use the 'Clear interrupt 1' command.

#### 3.6.3 Read downlink messages

A part of the X data memory is reserved for a downlink message. This part is referred to as RX payload. The RX payload buffer occupies 9 x 24-bit words and starts at the address location described in 0

The RX payload buffer contains 2 items:

- Downlink payload length:

- o Defines the length of the downlink message in bits.

- The downlink message length occupies the first 24-bit word of the payload buffer.

- Downlink message

- o Downlink message as defined by ARGOS standard A4-SYS-IF-0086-CNES, see Table 17.

- o Starts at the second 24-bit word of the payload buffer.

- The first bit of the Downlink message is aligned with the MSB of the second 24-bit word of the payload buffer. Bit 25 of the Downlink message is aligned with the MSB of the third 24-bit word of the payload buffer. In this way the total Downlink message occupies a number of consecutive 24-bit words in the payload buffer.

- In case the total length of the Downlink message is not a multiple of 24 bits, the last used 24-bit word of the payload buffer is stuffed by the DSP with 0's at the LSB locations.

| Table 17 - Down | link message | format |

|-----------------|--------------|--------|

|-----------------|--------------|--------|

| Addressee<br>Identification | A-DCS<br>@ | Service | Data                               | FCS     |

|-----------------------------|------------|---------|------------------------------------|---------|

| 28 bits                     | 4 bits     | 8 bits  | $n x 8 (with 2 \le n \le 17 bits)$ | 16 bits |

#### 3.6.4 Configuring timeouts

Instructions like "Start reception for fixed time" and "Satellite detection" have a programmable timeout. Values are in seconds, maximum timeout is 2^20 seconds. See 3.4 for the memory locations.

| Table 18 - De | fault timeout | s values |

|---------------|---------------|----------|

|---------------|---------------|----------|

| Parameter                      | Unit    | Default |

|--------------------------------|---------|---------|

| RX Timeout                     | Seconds | 10      |

| Satellite Detection<br>Timeout | Seconds | 2       |

### 3.7 CRC Check

During the firmware boot process a CRC is calculated on the memories. The MCU can check these values with the CRC results supplied by the firmware of the ARTIC to ensure that the downloaded content is correct.

When initialization (and CRC check) is finished, INT 1 is set. At this time the MCU can read the CRC checksum results and compare them against the reference values, which are provided with the firmware files.

There are 3 x 24-bit checksums which can be read back from XMEM. See 3.4 for the 'CRC results' memory location

| Address<br>offset [word] | Content              |

|--------------------------|----------------------|

| 0                        | P memory CRC results |

| 1                        | X memory CRC results |

| 2                        | Y memory CRC results |

#### Table 19 - CRC results map

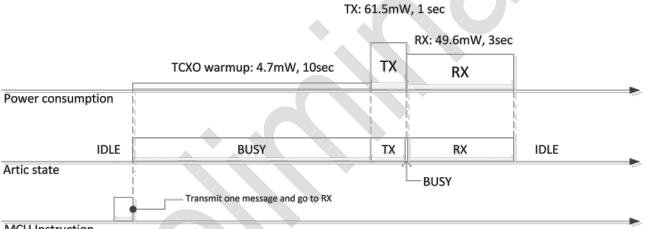

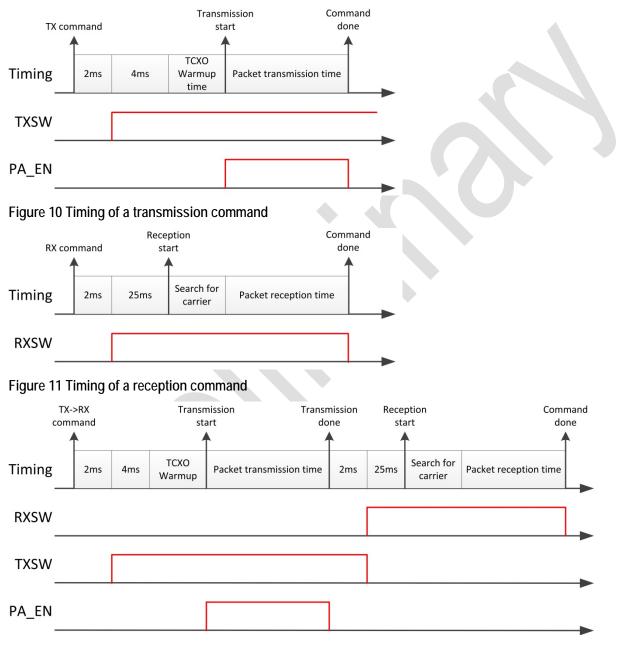

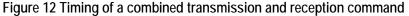

### 3.8 Firmware version